Bus I2C: assegnazione, dispositivo, trasferimento dati, indirizzamento

Durante la creazione di un circuito elettronico, molti sviluppatori si trovano di fronte alla necessità di utilizzare un gran numero di chip intermedi per abbinare, campionare e indirizzare i suoi singoli blocchi. Per ridurre al minimo il numero di chip ausiliari, negli anni '80 Philips ha proposto un'interfaccia di rete seriale I2C bidirezionale a due fili, progettata specificamente per gestire più chip all'interno di un singolo dispositivo.

Oggi, la sola Philips produce più di cento dispositivi compatibili I2C per apparecchiature elettroniche con un'ampia varietà di scopi: memoria, sistemi di processori video, convertitori analogico-digitale e digitale-analogico, driver display, ecc.

Il bus I2C è una modifica del protocollo di scambio dati seriale in grado di trasmettere dati seriali a 8 bit nella consueta modalità "veloce" a velocità comprese tra 100 e 400 kbps. Il processo di scambio dei dati è implementato qui solo su due fili (senza contare il filo comune): linea SDA per i dati e linea SCL per la sincronizzazione.

Il bus diventa bidirezionale per il fatto che le cascate di uscite dei dispositivi collegati al bus hanno collettori o canali aperti, replicando così il cablaggio AND. Di conseguenza, il bus riduce al minimo il numero di connessioni tra i chip, lasciando meno pin e tracce necessari sulla scheda. Di conseguenza, la scheda stessa risulta essere più semplice, più compatta e tecnologicamente più avanzata nella produzione.

Questo protocollo consente di disabilitare i decodificatori di indirizzi e altra logica di negoziazione esterna. Il numero di chip che possono operare contemporaneamente sul bus I2C è limitato dalla sua capacità, un massimo di 400 pF.

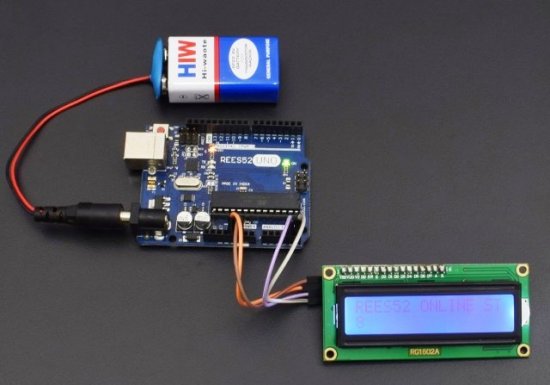

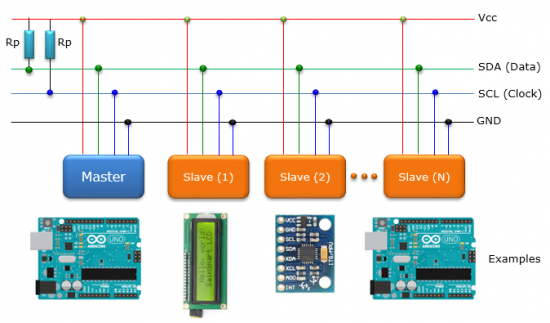

I circuiti integrati compatibili con I2C dispongono di un algoritmo di soppressione del rumore hardware per garantire l'integrità dei dati anche in presenza di forti interferenze. Tali dispositivi hanno un'interfaccia che consente ai microcircuiti di comunicare tra loro anche quando le loro tensioni di alimentazione sono diverse. Nella figura seguente, puoi familiarizzare con il principio del collegamento di più microcircuiti tramite un bus comune.

Ciascuno dei dispositivi collegati al bus ha un proprio indirizzo univoco, è determinato da esso e, in base allo scopo del dispositivo, può funzionare come ricevitore o come trasmettitore. Durante la trasmissione dei dati, questi dispositivi possono essere master (master) o slave (slave). Il master è il dispositivo che avvia il trasferimento dei dati e genera segnali di clock sulla linea SCL. Lo slave, rispetto al master, è il dispositivo di destinazione.

In un dato momento di funzionamento sul bus I2C, solo un dispositivo può fungere da master; genera un segnale sulla linea SCL.Un master può essere un ricevitore master o un trasmettitore master.

In linea di principio, il bus consente diversi master, ma impone restrizioni sulle caratteristiche di formazione dei segnali di controllo e sul monitoraggio dello stato del bus; questo significa che più master possono iniziare a trasmettere contemporaneamente, ma conflitti di questo tipo vengono eliminati grazie all'arbitrato, cioè al modo in cui il master si comporta quando rileva che il bus è occupato da un altro master.

La sincronizzazione di una coppia di dispositivi è assicurata dal fatto che tutti i dispositivi sono collegati al bus formando un cablaggio "AND". Inizialmente, i segnali SDA e SCL sono alti.

START e STOP

Lo scambio inizia con il master che genera lo stato «START»: sulla linea SDA il segnale passa dallo stato alto a quello basso, mentre la linea SCL ha un livello alto stabile. Tutti i dispositivi collegati al bus percepiscono questa situazione come un comando per avviare lo scambio.

Ogni master genera un segnale di clock individuale sulla linea SCL durante la trasmissione dei dati sul bus.

Lo scambio termina con la formazione dello stato di STOP da parte del master: sulla linea SDA il segnale passa da basso ad alto, mentre la linea SCL ha un livello alto stabile.

Il conducente funge sempre da fonte dei segnali START e STOP. Non appena il segnale «START» è fisso, significa che la linea è occupata. La linea è libera quando viene rilevato un segnale di STOP.

Subito dopo aver dichiarato lo stato START, il master commuta la linea SCL a livello basso e invia il bit più significativo del primo byte del messaggio alla linea SDA. Il numero di byte in un messaggio non è limitato.Le modifiche sulla linea SDA sono abilitate solo quando il livello del segnale sulla linea SCL è basso. I dati sono validi e non devono essere modificati solo quando l'impulso di sincronizzazione è alto.

Il riconoscimento che il byte dal trasmettitore master è stato ricevuto dal ricevitore slave viene effettuato impostando uno speciale bit di riconoscimento sulla linea SDA dopo che è stato ricevuto l'ottavo bit di dati.

LA CONFERMA

Quindi, l'invio di 8 bit di dati dal trasmettitore al ricevitore finisce con un impulso extra sulla linea SCL quando il dispositivo ricevente diventa basso sulla linea SDA, indicando che ha ricevuto l'intero byte.

La conferma è parte integrante del processo di trasferimento dei dati. Il master genera un impulso di sincronizzazione. Il trasmettitore invia uno stato basso a SDA mentre il clock di riconoscimento è attivo. Mentre l'impulso di sincronismo è alto, il ricevitore deve mantenere basso l'SDA.

Se lo slave di destinazione non riconosce il suo indirizzo, ad esempio perché è attualmente occupato, la linea dati deve essere tenuta alta. Il master può quindi dare un segnale di STOP per interrompere l'invio.

Se la ricezione viene eseguita dal ricevitore master, è obbligato a informare il trasmettitore slave dopo il completamento della trasmissione, non confermando l'ultimo byte. Il trasmettitore slave rilascia la linea dati in modo che il master possa emettere un segnale STOP o un segnale START ripetuto.

La sincronizzazione dei dispositivi è garantita dal fatto che i collegamenti alla linea SCL sono realizzati secondo il principio "AND".

Il master non ha il diritto esclusivo di controllare la transizione della linea SCL dal basso all'alto.Se lo slave ha bisogno di più tempo per elaborare un bit ricevuto, può mantenere SCL basso in modo indipendente fino a quando non è pronto a ricevere il successivo bit di dati. La linea SCL in tale situazione sarà bassa per la durata dell'impulso di sincronismo di basso livello più lungo.

I dispositivi con il minimo sostenuto più basso rimarranno inattivi fino al termine del lungo periodo. Quando tutti i dispositivi hanno terminato il periodo di sincronizzazione basso, SCL aumenterà.

Tutti i dispositivi inizieranno a registrare un clock alto e il primo dispositivo a completare il periodo sarà il primo a impostare la linea SCL bassa. Di conseguenza, la durata dello stato basso di SCL sarà determinata dallo stato basso più lungo dell'impulso di sincronizzazione di uno dei dispositivi e la durata dello stato alto sarà determinata dal periodo di sincronizzazione più breve di uno dei dispositivi dispositivi.

I segnali di sincronizzazione possono essere utilizzati dai ricevitori come mezzo per controllare la trasmissione dei dati a livello di bit e byte.

Se il dispositivo è in grado di ricevere byte a una velocità elevata, ma ci vuole un certo periodo di tempo per memorizzare il byte ricevuto o prepararsi a ricevere il byte successivo, potrebbe continuare a mantenere basso SCL dopo aver ricevuto e riconosciuto un byte, forzando il trasmettitore in uno stato di standby.

Un microcontrollore senza circuiti hardware incorporati, ad esempio a livello di bit, può rallentare la velocità di clock aumentando la durata del loro stato basso.Di conseguenza, il baud rate del dispositivo master sarà determinato dalla velocità del dispositivo più lento.

INDIRIZZAMENTO

Ogni dispositivo connesso al bus I2C ha un indirizzo di programma univoco al quale il master lo indirizza inviando un comando specifico. Microcircuiti dello stesso tipo sono caratterizzati da un selettore di indirizzo, implementato sotto forma di ingressi digitali del selettore o in forma analogica. Gli indirizzi sono suddivisi nello spazio degli indirizzi dei dispositivi collegati al bus.

La modalità normale presuppone l'indirizzamento a sette bit. L'indirizzamento funziona come segue: dopo il comando «START», il master invia il primo byte, che determina quale dispositivo slave è necessario per comunicare con il master. Esiste anche un indirizzo di chiamata comune che definisce tutti i dispositivi sul bus, tutti i dispositivi (teoricamente) rispondono con un riconoscimento, ma in pratica questo è raro.

Quindi i primi sette bit del primo byte sono l'indirizzo dello slave. Il bit meno significativo, l'ottavo, indica la direzione di invio dei dati. Se è presente uno «0», le informazioni verranno scritte dal master a questo slave. Se «1», le informazioni verranno lette dal master da questo slave.

Dopo che il master ha finito di inviare il byte dell'indirizzo, ogni slave confronta il proprio indirizzo con esso. Chiunque abbia lo stesso indirizzo è uno slave e viene definito slave trasmittente o slave ricevente, a seconda del valore del bit meno significativo del byte dell'indirizzo.

Un indirizzo slave può includere parti fisse e programmabili. Molto spesso un numero elevato di dispositivi dello stesso tipo funziona in un sistema, quindi la parte programmabile dell'indirizzo consente l'utilizzo di un massimo dello stesso tipo di dispositivi sul bus. Quanti bit nel byte dell'indirizzo sono programmabili dipende dal numero di pin liberi sul chip.

A volte è sufficiente un pin con un'impostazione analogica dell'intervallo di indirizzi programmabili, ad esempio SAA1064, un driver indicatore LED che ha esattamente tale implementazione. Il potenziale di un particolare pin determina l'offset dello spazio degli indirizzi del chip in modo che i chip dello stesso tipo non entrino in conflitto operando sullo stesso bus. Tutti i chip che supportano il bus I2C contengono una serie di indirizzi specificati dal produttore nella documentazione.

La combinazione «11110XX» è riservata all'indirizzamento a 10 bit. Se immaginiamo lo scambio di dati dal comando «START» al comando «STOP», sarà simile a questo:

Qui sono consentiti formati di scambio di dati semplici e combinati. Il formato combinato significa che tra «START» e «STOP» il master e lo slave possono fungere da ricevitori e trasmettitori, questo è utile ad esempio nella gestione della memoria seriale.

Lascia che il primo byte di dati trasferisca un indirizzo di memoria. Quindi, ripetendo il comando «START» e leggendo l'indirizzo dello slave, i dati della memoria funzioneranno. Le decisioni di incrementare o decrementare automaticamente l'indirizzo a cui si è avuto accesso in precedenza vengono prese dallo sviluppatore del dispositivo dopo aver studiato in precedenza la documentazione del chip. In un modo o nell'altro, dopo aver ricevuto il comando START, tutti i dispositivi devono ripristinare la loro logica e prepararsi al fatto che l'indirizzo verrà ora nominato.